| client (0.6.2 anago only) | 2010-11-19 20:00 |

| kazzo (0.1.3) | 2010-03-13 00:09 |

60pin edge connecter 経由で書き込み信号を送る際に問題となる点は下記の3点です。

ROM 領域 ($8000-$ffff) の read は ROM のデータですが、ほとんどのカセット(マッパ)で write はバンク切り替えの制御用アドレスになっています。flash memory へデータを書き込むときは write 信号を送る必要があり、一見矛盾します。

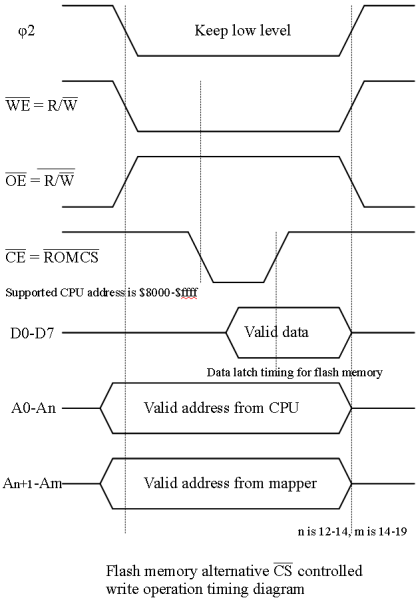

flash memory の制御線には CS (Chip Select), WE (Write Enable), OE (Output Enable)があります。flash memory は /CS:L and /OE:H and /WE の立ち上がりまたは /WE:L and /OE:H and /CS の立ち上がりで書き込みデータを取得します。

対して 6502 の制御線は R/W (read or write), φ2 (machine cycle) で構成されており、マッパは /ROMCS:L and R/W: L and φ2 の立ち下がりで書き込みデータを取得します(例外有り)。

flash memory が write と認識する条件と、マッパが write が認識する条件がことなることを利用して、flash memory へ書き込むときはφ2を動かさないことによりバンク切り替えの暴発を防ぐことが出来ます。

flash memory はアドレスバス A0-A14 が 0x2aaa, 0x5555 へ指定のコマンドを書き込むと ROM 以外の処理が行えます。これを利用してデータを書き込みます。バンクの仕様はハードによってばらばらなので、個別に辻褄を合わせる必要があります。

詳細はソフトウェア編に記載します。

74xx161 などで構成されている単純なハードウェアでは ROM の制御線の接続が不十分でデータバスが ROM と CPU 両方からデータが出ることになり、データが不安定になる可能性があります。

ROM を接続する場合は 74xx161 が認識する程度の安定したデータを送ればいいのに対し、 flash memory では RAM 同様の制御線を接続する必要があります。

MMCx などカスタムチップの場合は制御線を構成しなおしているものがほとんどでこの問題はありません。カスタムチップから /OE と /CS を混合した制御線が1本でています。

R/W CPU /ROMCS|memory /enable L L |H L H |H H L |L H H |H

アドレスバス、データバスについては ROM と同様の接続でよいです。あまってしまう上位アドレスバスは GND か +5V (どちらでもよいので配線しやすい方を選ぶ)で入力を固定してください。

/CS はアドレスデコード部分が入っていればよいので、 /ROMCS を接続します。$6000-$7fff が ROM になっているまれなカセットはうまくいかないと思います。

/WE には R/W を接続します。

ROM の場合 /OE と /CS が混合されているのでこれを分離します。Output Enable は R/W:H (read) 時に /OE が L になればよいので、 R/W の反転を接続します。

カスタムチップの場合は /ROMCS 成分が入ってますが、辻褄はあうので ROM enable 信号を接続します。

データバスとアドレスバスは CPU area (Program Memory) と同じです。 PPU area の制御線は CPU に比べてとても素直で、バンク切り替え暴発がないので単純です。RAM と同じく下記の配線にしてください。

注意する点は下記です。